Foreground Detector

Features

- An IP core for field-programmable gate arrays.

- Detects image foreground based on statistical processing of historical image data.

- Uses only on-chip BRAMs. No external framebuffer required.

- Compatible with data streaming interfaces.

- Designed specifically to minimize resource requirements.

- Available for resolutions from 640x480 to 1920x1080.

The foreground detector uses a statistical algorithm based on down-scaling of the resolution of a processed image while minimizing loss of information through selecting a suitable pixel aggregation. The quality of the algorithm is comparable to the Mixture-of-Gaussians algorithm for standard image datasets. The IP core was designed to use only minimum of FPGA resources.

Implementation Data for XC7Z020-3CLG484

| Resolution | 640x480 | 704x576 | 1280x1080 | 1920x1080 |

|---|---|---|---|---|

| Slices | 1748 | 1713 | 1885 | 1874 |

| Slice registers | 1369 | 1235 | 1260 | 1254 |

| RAMB18E1s | 10 | 10 | 4 | 0 |

| RAMB36E1s | 13 | 13 | 45 | 66 |

| DSP48E1s | 24 | 24 | 26 | 26 |

| Minimum period [ns] | 13.917 | 13.283 | 13.179 | 14.129 |

| Running frequency [MHz] | 71 | 75 | 75 | 70 |

| Frame rate [fps] | 234 | 185 | 54 | 34 |

Application Areas

Any applications that require customized feature detection or extraction, such as

- Video surveillance

- Access control

- Traffic monitoring

Application Example

A sample image from the highway dataset and the corresponding

foreground mask detected by the foreground detector IP core.

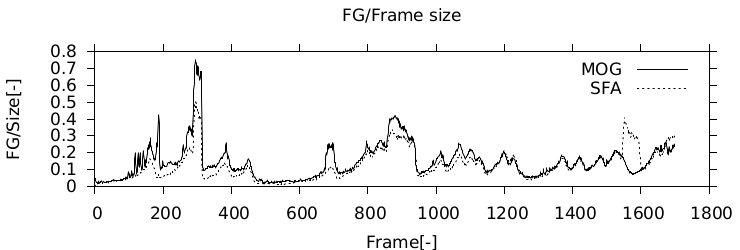

The foreground detector (SFA series) compared to the MoG algorithm (MOG series) for the highway dataset.

The graph shows foreground masks detected in time as a percentage of pixels in the whole image.

The highway dataset can be downloaded from the changedetection.net website.